## Questions de cours

1. Simplifiez l'expression Booléenne suivante : (1 point)

$$A = a \cdot b + \overline{(b + \overline{a} \cdot b) \cdot \overline{c}}$$

2. La sortie d'une porte A doit être branchée à l'entrée d'une porte logique B. Étant donné l'extrait des spécifications techniques reproduit ci-dessous, a-t-on la garantie que le circuit se comportera correctement, donc que la porte B interprétera correctement les niveaux logiques en sortie de la porte A? Justifiez votre réponse. (1 point)

|                     |                           | $\mathbf{porte}\ A$ |     |      | $\mathbf{porte}\ B$ |     |      |

|---------------------|---------------------------|---------------------|-----|------|---------------------|-----|------|

|                     |                           | MIN                 | MAX | UNIT | MIN                 | MAX | UNIT |

| $\overline{V_{IH}}$ | High-level input voltage  | 2                   |     | V    | 3.5                 |     | V    |

| $V_{IL}$            | Low-level input voltage   |                     | 0.8 | V    |                     | 0.7 | V    |

| $V_{OH}$            | High-level output voltage | 3                   |     | V    | 4                   |     | V    |

| $V_{OL}$            | Low-level output voltage  |                     | 0.4 | V    |                     | 0.3 | V    |

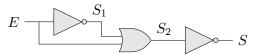

3. Exprimez la valeur de la sortie S du circuit ci-dessous en fonction de son entrée E. Simplifiez l'expression et commentez-là. (1 point)

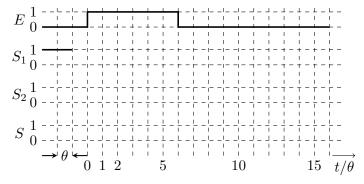

4. Le temps de passage (ou délai de propagation) d'une porte logique est la durée entre l'instant où les signaux sont appliqués à l'entrée et celui où leur effet se répercute en sortie. Pour la suite nous allons supposer qu'un inverseur possède un temps de passage  $3\theta$ , tandis que le temps de passage d'une porte à deux entrées vaut  $2\theta$ . On considère la conséquence d'une impulsion à l'entrée du circuit de la question 3: l'entrée E, longtemps restée à 0, passe de 0 à 1 au temps t=0, et de 1 à 0 au temps  $t=6\theta$ , pour rester ensuite à 0.

Dessinez dans votre copie un chronographe semblable à celui ci-dessous, montrant l'évolution de  $E, S_1, S_2$  et S entre  $t = -3\theta$  et  $t = 16\theta$ . Commentez le comportement du circuit. (2 points)

- 5. Expliquez la contradiction apparente entre le résultat de la question 3 et le chronographe que vous avez construit à la question 4. (1 point)

- 6. Quelle pourrait être l'utilité pratique du circuit ci-dessus? (1 point)

- 7. a) Rappelez le tableau de vérité d'un additionneur élémentaire prenant deux bits (a, b) et une retenue r en entrée, et affichant en sortie la somme a+b+r en notation binaire sur 2 bits  $(R\Sigma)$ . Ici  $\Sigma$  représente le chiffre de poids faible de la somme (la somme modulo 2), R le chiffre de poids fort (la retenue à reporter). (1 point)

- b) À partir d'un tel additionneur élémentaire, qu'on représentera par le symbole suivant :

dessiner le schéma d'un additionneur de deux mots de 4 bits. (1 point)

c) En supposant qu'un additionneur élémentaire met 40 ns à calculer les sorties  $(\Sigma, R)$ , combien de temps faut-il à l'additionneur complet à 4 bits pour afficher une sortie valide après un changement des entrées? (1 point)

## Circuit séquentiel

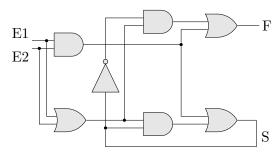

Dans cet exercice il s'agit d'analyser le circuit suivant, et de décrire son comportement.

- 8. À quoi voit-on que ce circuit logique est séquentiel et non pas simplement combinatoire? (1 point)

- 9. Proposez une variable interne adaptée et expliquez pourquoi une seule suffit. (1 point)

- 10. Écrivez le tableau de Karnaugh de la fonction d'excitation pour la sortie correspondante du circuit d'excitation. (1 point)

- 11. Qu'est-ce qui caractérise de manière générale un état stable du d'un système séquentiel? Identifiez dans le tableau de Karnaugh de la question précédente les six états stables du système ci-dessus et numérotez-les. (2 points)

- 12. Tracez le graphe de fluence du circuit, donc un graphe où les différents états stables sont représentés par des nœuds, reliés par des flèches indiquant les transitions possibles entre ceux-ci. (2 points)

- 13. Expliquez pourquoi la séquence d'entrées  $(E_1E_2)$  suivante :  $(00)\rightarrow(01)\rightarrow(00)\rightarrow(10)\rightarrow(11)\rightarrow(10)\rightarrow(11)\rightarrow(01)\rightarrow(11)$  engendre une sortie qui commence par les valeurs

$$(0) \rightarrow (1) \rightarrow (0) \rightarrow (1) \rightarrow (1) \rightarrow (0) \rightarrow (a) \rightarrow (b) \rightarrow (c).$$

Comment voit-on à cette séquence qu'il s'agit de la sortie d'un circuit séquentiel et non d'un circuit combinatoire? Que valent les trois dernières valeurs a,b et c de cette séquence? (3 points)